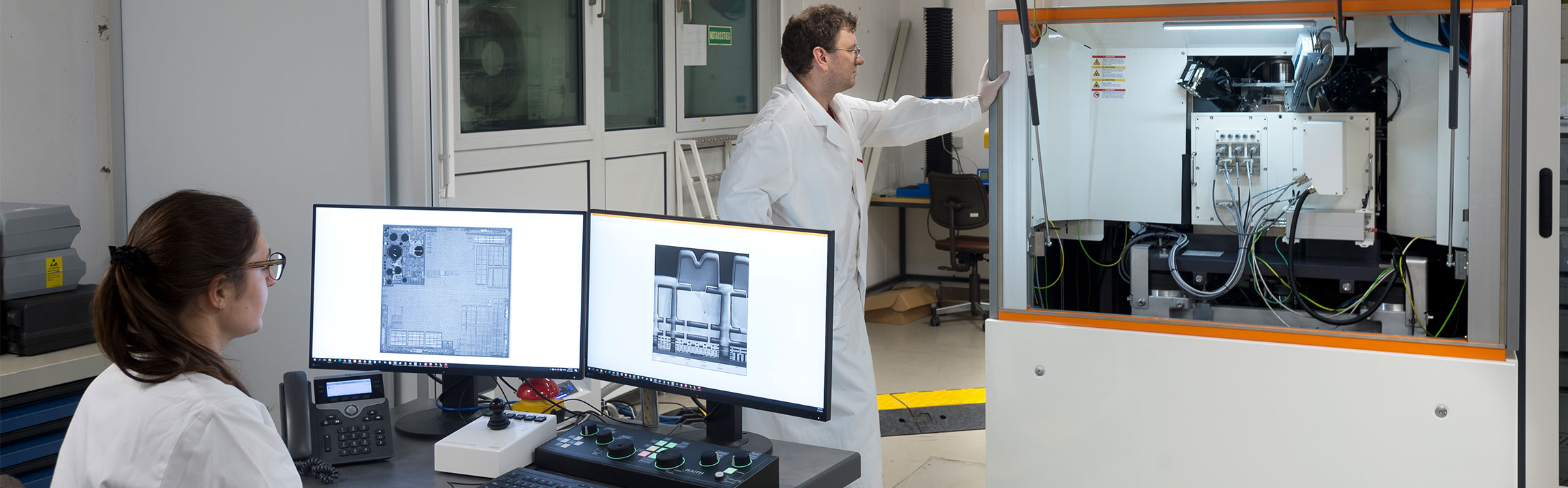

Wir bieten nicht nur Analysen auf Systemebene an, sondern auch weiterführende Analysen auf Bauteillevel. Mit modernsten Tools überprüfen wir die Einzelkomponenten auf Zuverlässigkeit, Originalität, IP-Verletzungen und Fehleranalyse. Unser Sicherheitslabor ist nach Common Criteria – Evaluation Assurance Level 6 (CC-EAL6) zertifiziert und ermöglicht uns auch die Untersuchung sicherheitsrelevanter Bausteine. Durch eine vollflächige planare Präparation der Metalllagen eines IC und anschließendem Chipscan können wir diese mithilfe einer GDSII-Konversion auf IP-Verletzungen und Verdacht auf maligne Manipulation der Schaltung überprüfen.

Fehleranalyse und Authentizitätsprüfung auf Package- & Chiplevel

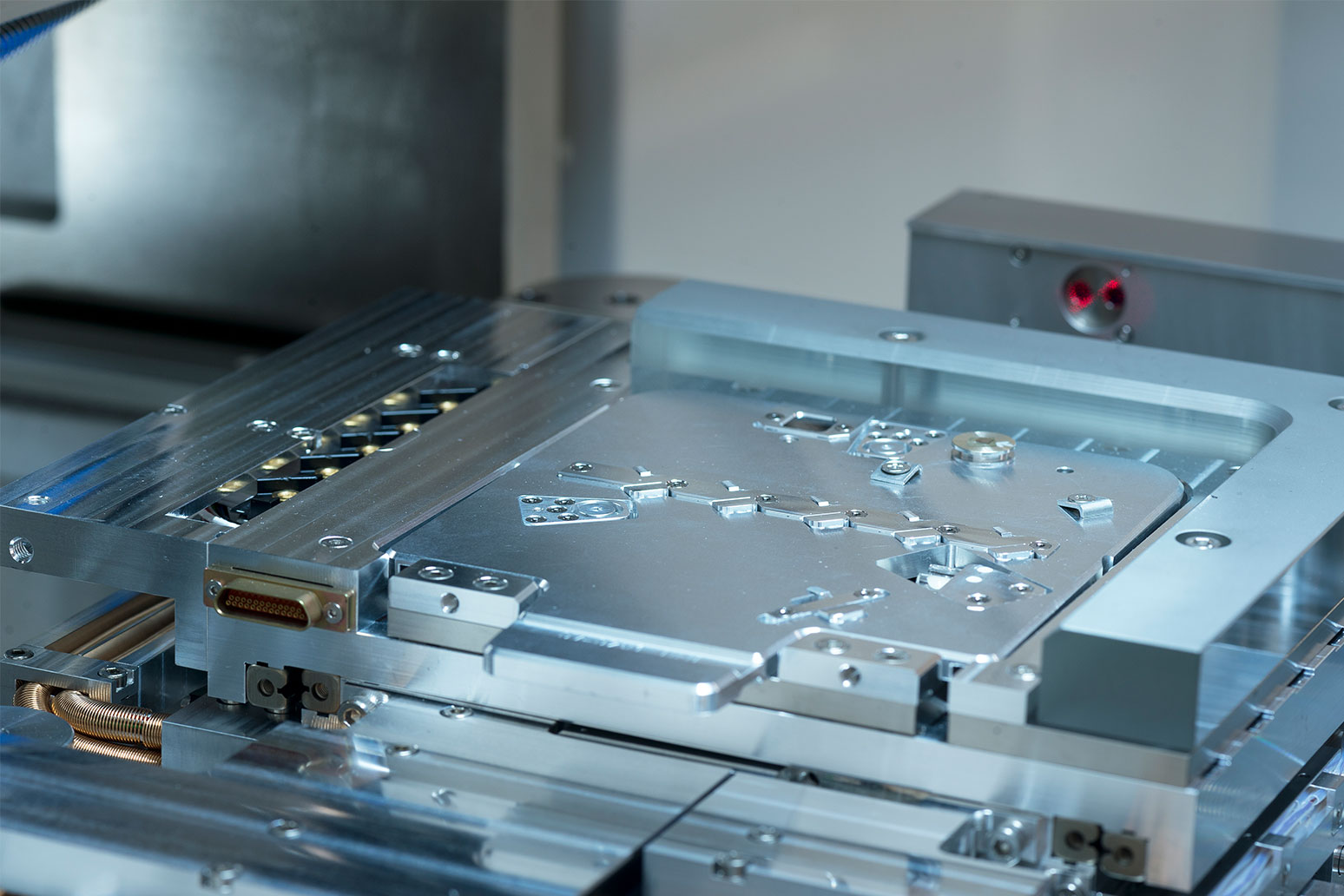

Ansicht der Raith Velion FIB-SEM bei geöffnetem Front Cover

Leistungen im Bereich Package- & Chiplevel-Analysen

Analysen auf Bauteillevel

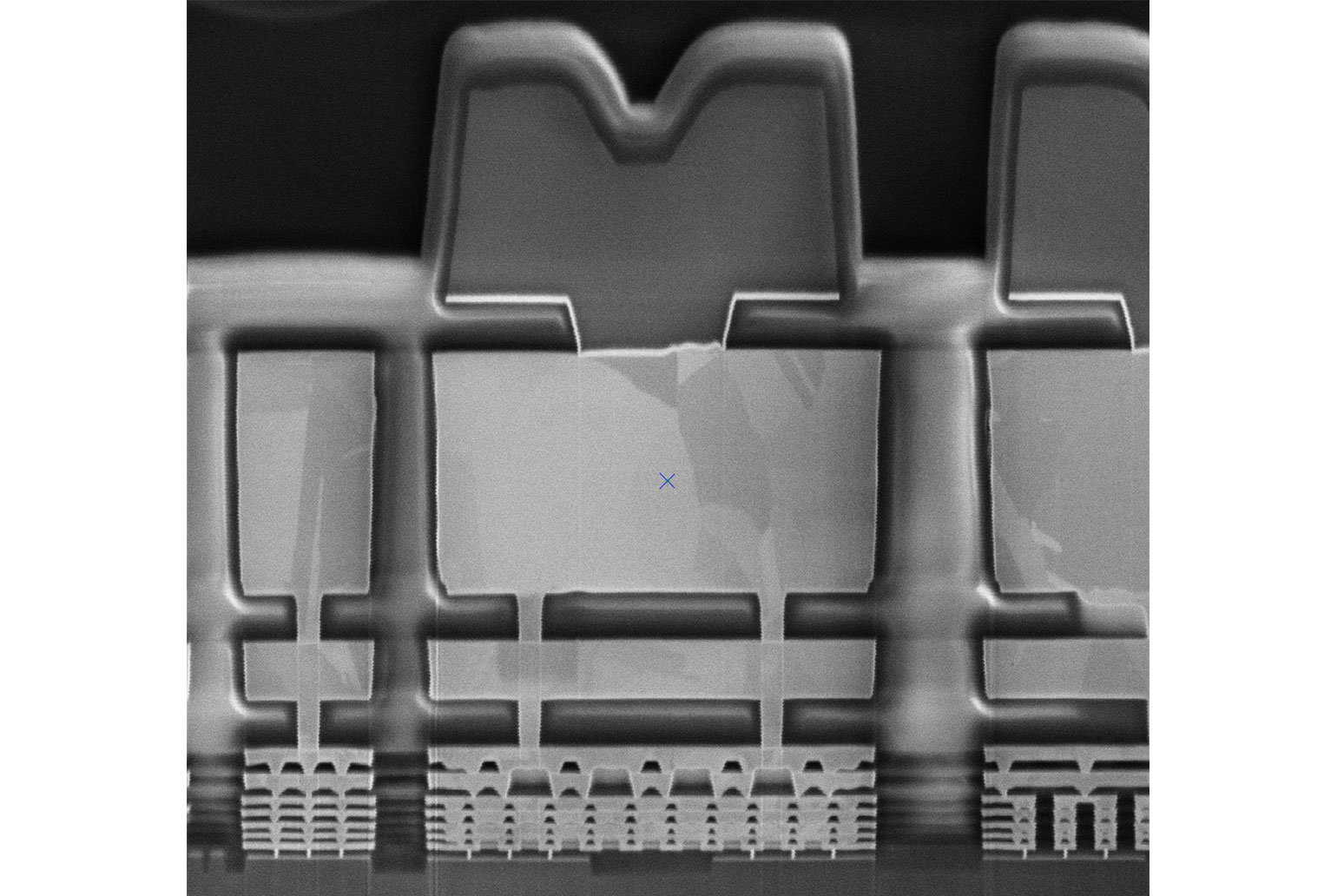

- Fehler- und Schadensanalyse mittels lichtoptischer- und Röntgeninspektion, metallografischer Schliffpräparation sowie Rasterelektronenmikroskop, sowie elektrischer Messung auf IC-Level

- Modernste Tools zur Einzelkomponentenanalyse hinsichtlich Zuverlässigkeit, Originalität, IP-Verletzung

- Sicherheitslabor zertifiziert nach Common Criteria – Evaluation Assurance Level 6 (CC-EAL6) für Untersuchung sicherheitsrelevanter Bausteine

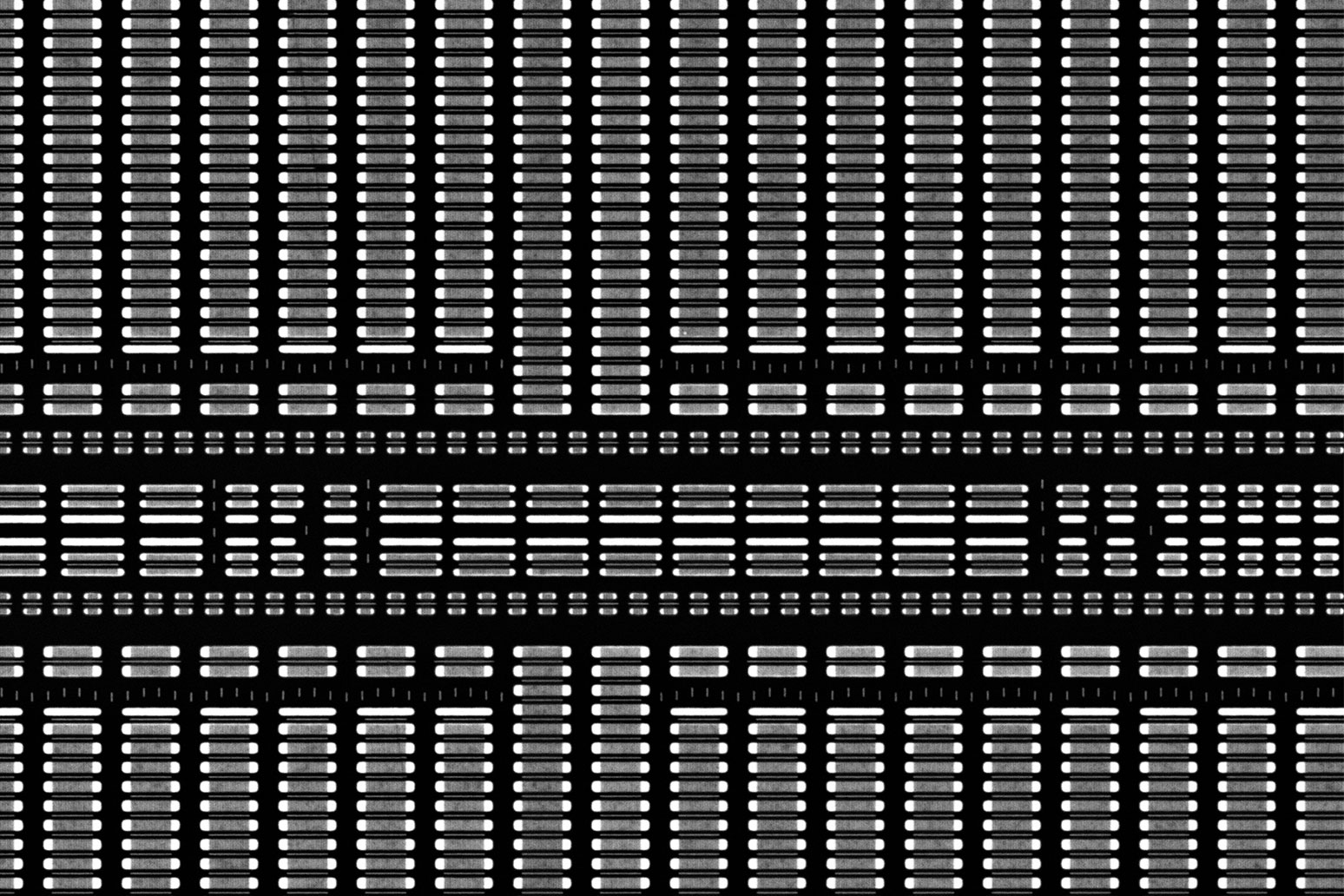

- Vollflächige planare Präparation einzelner Metalllagen eines IC mit GDSII-Konversion und Untersuchung auf IP-Verletzung oder maligne Manipulation

- Tiefergehende Analyse zur Robustheit und ESD-Untersuchungen in Kooperation mit der Expertengruppe der elektrischen Messtechnik

Services auf Komponentenlevel

- Elektrische Charakterisierung von SMD Komponenenten

- Originalitätsprüfung von IC und Packages

- IC-Technologieanalyse

- De-Packaging

- De-Prozessierung von IC: von aktiver Seite (De-Layering) oder rückseitig (Chipdünnen)

- Vollflächige Rasterelektronenmikroskopie-Aufnahme ganzer Metallisierungslagen und deren Präparation

- Patentanalyse

Tiefergehende Analysen hinsichtlich Robustheit und ESD-Untersuchungen bieten wir in enger Kooperation mit unserer Expertengruppe der elektrischen Messtechnik an.

Sie wollen mehr über Package- & Chiplevel-Analysen in der Praxis erfahren?

Dann nehmen Sie mit uns Kontakt auf!