Das Fraunhofer EMFT ist seit 30 Jahren führend in der Erforschung und Anwendung von Elektrostatischen Entladungen (ESD) in der Mikroelektronik. Unsere Kompetenz umfasst die effiziente Lösung von akuten Problemen, die Qualifikation von Bauelementen mit speziellen Anforderungen und die Entwicklung zuverlässiger ESD-Schutzkonzepte für elektronische Schaltungen und Systeme. Als Mitglied des deutschen ESD-FORUM e.V. und der Standardisierungsausschüsse ESD-Test der ESD Association sind wir international anerkannt. In unserem Labor verwenden wir sowohl standardisierte als auch neu entwickelte Methoden und Systeme zur ESD-Prüfung und entwickeln maßgeschneiderte Testmethoden und -aufbauten für unsere Kunden. Unser erfahrenes Team und unsere erstklassige messtechnische Ausstattung ermöglichen uns, auch außergewöhnliche Testlösungen zu erarbeiten.

ESD Test und Prüfung

Elektrostatische Entladungen begegnen uns im Alltag oft häufiger als uns lieb ist – manchmal reicht die Berührung eines Türgriffs, um die unangenehmen Entladungen zu spüren. Verglichen mit elektronischen Systemen und Technologien reagiert der Mensch jedoch sehr unempfindlich, denn schon eine geringe Spannung kann vor allem bei High Speed Technologien schnell zu Schäden führen. Verstärkt wird diese Problematik noch durch den anhaltenden Trend der Miniaturisierung in der Mikroelektronik, was gleichzeitig zur Reduzierung der maximal zulässigen Entladungsspannung führt. Vor allem in automatisierten Produktionsumgebungen ist also ein ausreichender ESD-Schutz unbedingt erforderlich. Mit standardisierten Belastungsmodellen werden hierzu einzelne Bauteile auf ihre ESD-Festigkeit getestet. Jedoch stoßen gebräuchliche Testmethoden im Hinblick auf ihre Genauigkeit und Reproduzierbarkeit schon jetzt an ihre Grenzen, so dass genauere Messmethoden notwendig werden.

Charakterisierung von ESD-Schutzstrukturen

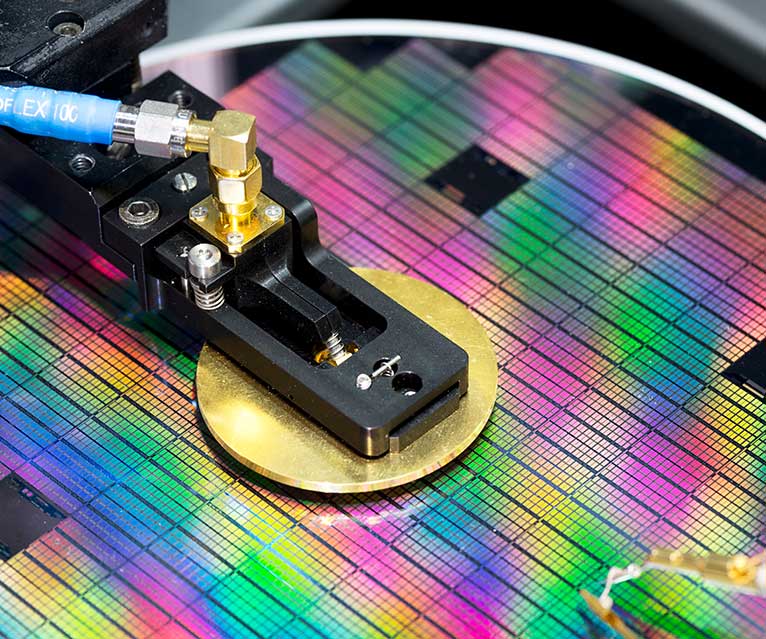

Im Auftrag verschiedener Industriekunden charakterisieren Forscherinnen des Fraunhofer EMFT ESD-Schutzstrukturen im ESD relevanten Hochstrombereich und mit einer transienten Auflösung von wenigen zehn Picosekunden. Auf Basis der Analyseergebnisse entwickeln die Experten leistungsfähige Schutzkonzepte für unterschiedliche Anwendungen und Anforderungen.

Für die Arbeiten kommen ein modernes vollausgebautes HPPI3011C TLP System in Verbindung mit einem 300 mm Cascade PA300 oder das HPPI ATS_8000A Flying Probe System in Verbindung mit breitbandigen Oszilloskopen (>33 GHz) von Keysight zum Einsatz.

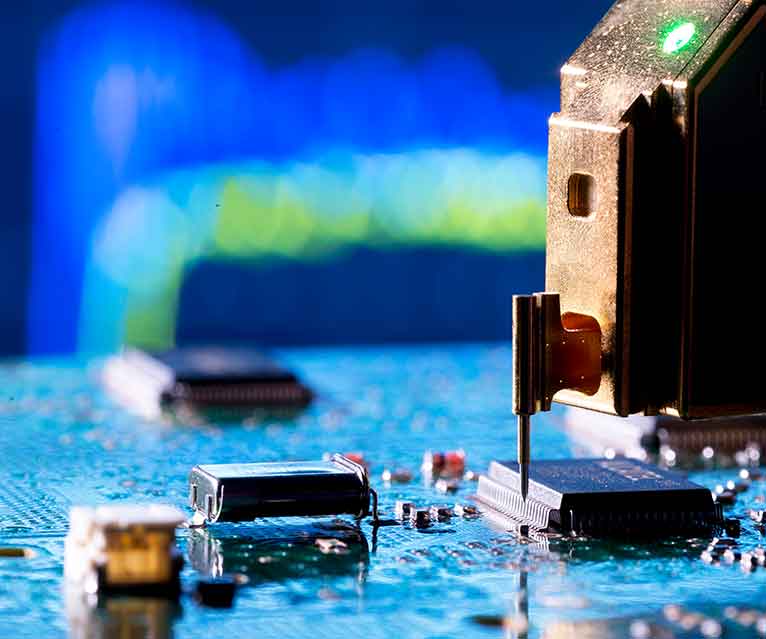

Für Industriepartner u.a. aus den Bereichen Automobil und LED-Beleuchtung werden ESD/ EOS-induzierte Ausfallszenarien reproduzierbar nachgebildet, Belastungen messtechnisch bis in den Pikosekunden-Bereich erfasst und deren Robustheit systematisch gesteigert.

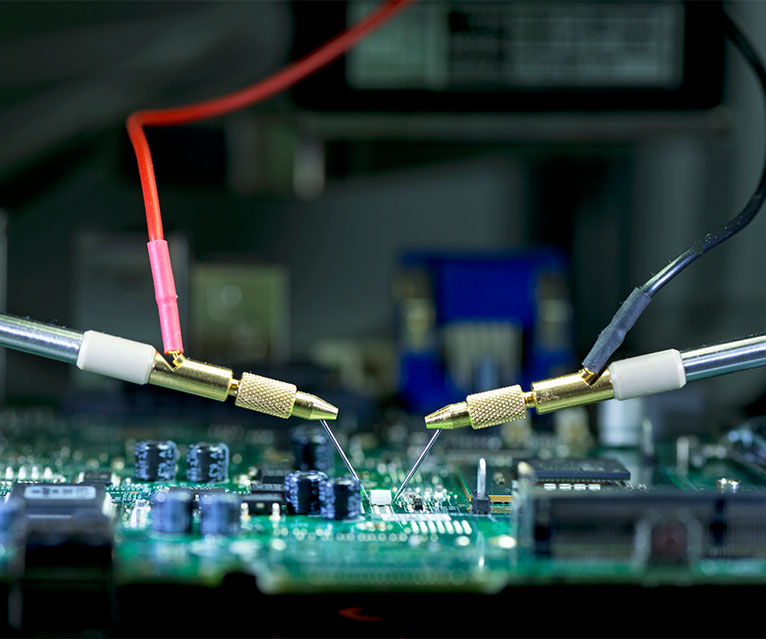

Auf Systemebene sind die Expertinnen und Experten des Fraunhofer EMFT darauf spezialisiert, auch designbedingte Störeffekte aufzuspüren und geeignete Schutzkonzepte zu entwickeln.

CC-TLP als neuer Standard für ESD Messungen

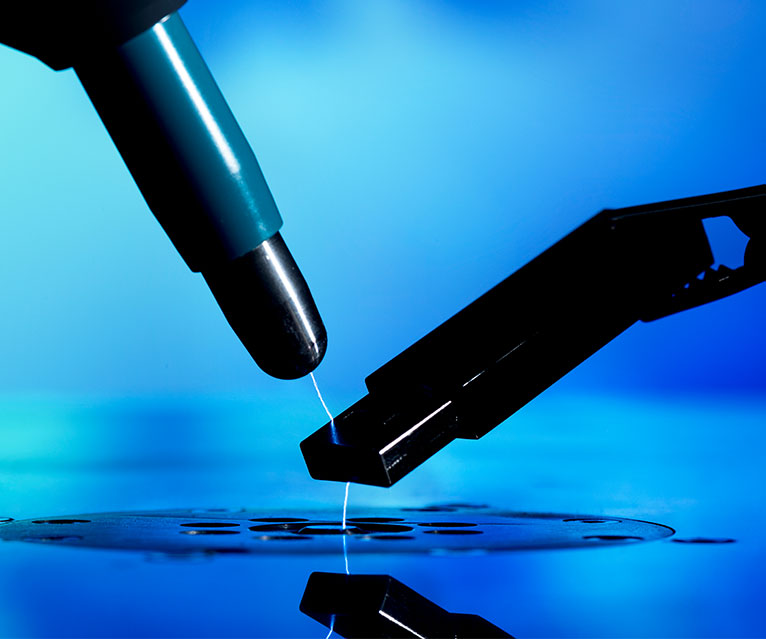

Mit dem so genannten Capacitively Coupled Transmission Line Pulsing (CC-TLP) haben die Forschenden eine neuartige Messtechnik entwickelt und patentiert, die bei der Bauteilprüfung eine wesentlich höhere Genauigkeit und Reproduzierbarkeit als der gebräuchliche CDM (Charged Device Model) Test aufweist. Dies ist vor allem bei modernen Technologien mit geringer ESD-Toleranz wichtig. Besonders nützlich ist auch die Möglichkeit, Schaltungen direkt auf einem Wafer testen zu können, so dass Schwächen im ESD-Schutz frühzeitig erkannt werden.

Im Oktober 2022 wurde CC-TLP als ein standardisiertes Verfahren für ESD-Tests unter ANSI/ESD SP5.3.4-2022 veröffentlicht.

Leistungen im Bereich ESD Untersuchungen und Qualifikation

- ESD Human Body Model (HBM) Test nach ANSI/ESDA/JEDEC JS-001-2023 auf Wafer/Die/Package Level (2-Pin HBM Tester)

- ESD Charged Device Model (CDM) Test nach ANSI/ESDA/JEDEC JS-002-2022

- ESD Hochstromcharakterisierung mit Transmission Line Pulsing (TLP) auf Wafer/Die/Package Level mit Impulslängen im sub ns bis in den µs Bereich bei verschiedenen Anstiegszeiten (ANSI/ESD STM5.5.1-2016).

- Capacitively Coupled TLP (CC-TLP) zur Evaluation der CDM-Festigkeit mit einer wesentlich höheren Genauigkeit und Reproduzierbarkeit (Standard Practice Document der ESDA veröffentlicht als ANSI/ESD SP5.3.4-2022)

- Human Metal Model (HMM) Messungen nach ESD SP5.6-2019

- System-Level ESD Untersuchungen angelehnt an IEC 61000-2-4

- Belastung von Schaltungen in Standardgehäusen, aber auch von Spezialgehäusen bis hin zu Bare Dies

EMV Messungen und Untersuchungen

- Scannermessungen der Abstrahlung von Produkten auf Boardlevel

- Messung der Empfindlichkeit von Systemen gegenüber Störeinstrahlungen (leitungs- oder nicht leitungsgebunden)

Sie wollen mehr über die Anwendungsmöglichkeiten im Bereich Elektrostatische Entladung - ESD - in der Praxis erfahren?

Dann nehmen Sie mit uns Kontakt auf!